(*The images displayed above are for advertising purpose and may contain excluded accessories. To learn about the kit content & included accesories, please refer to the information provided in "kit content" tab.)

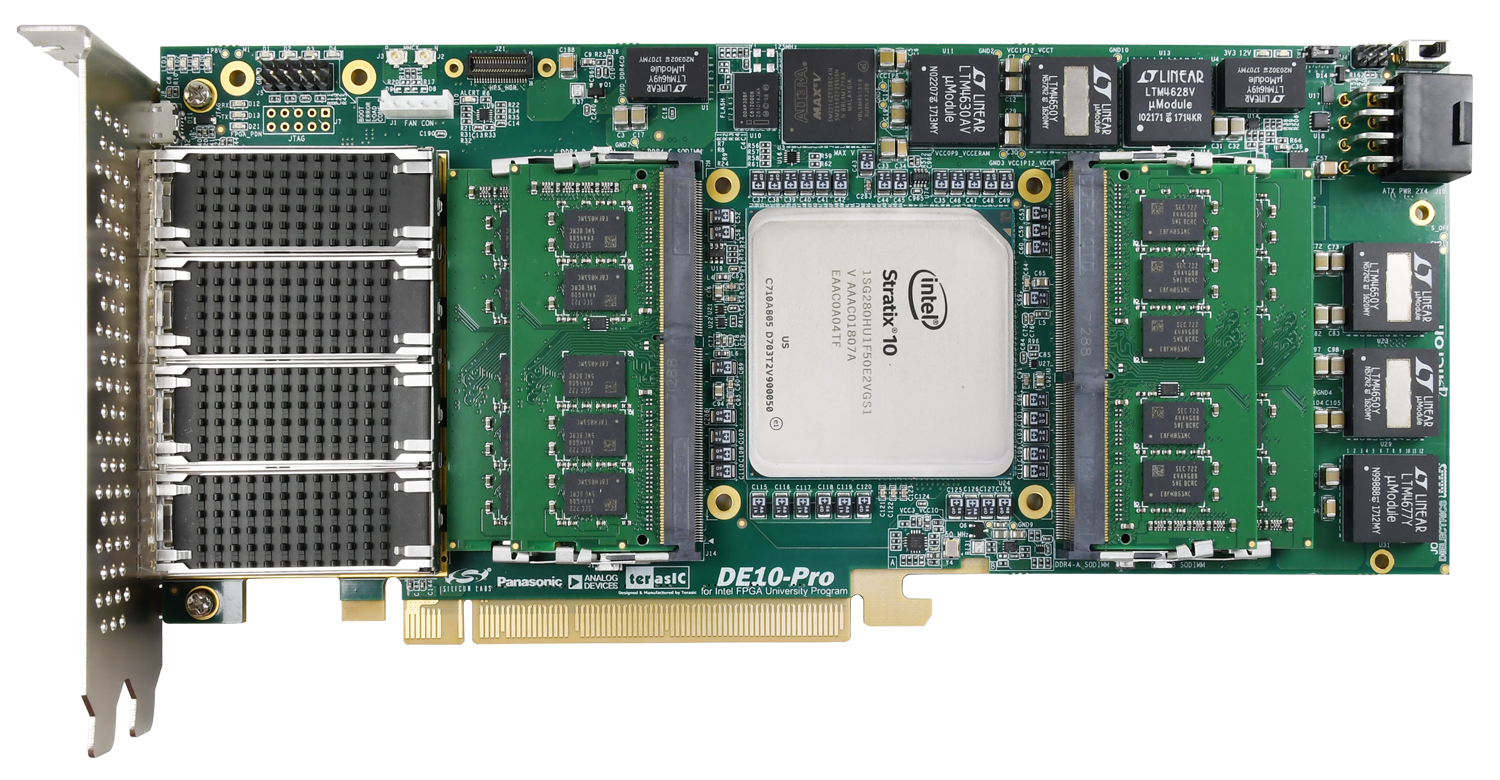

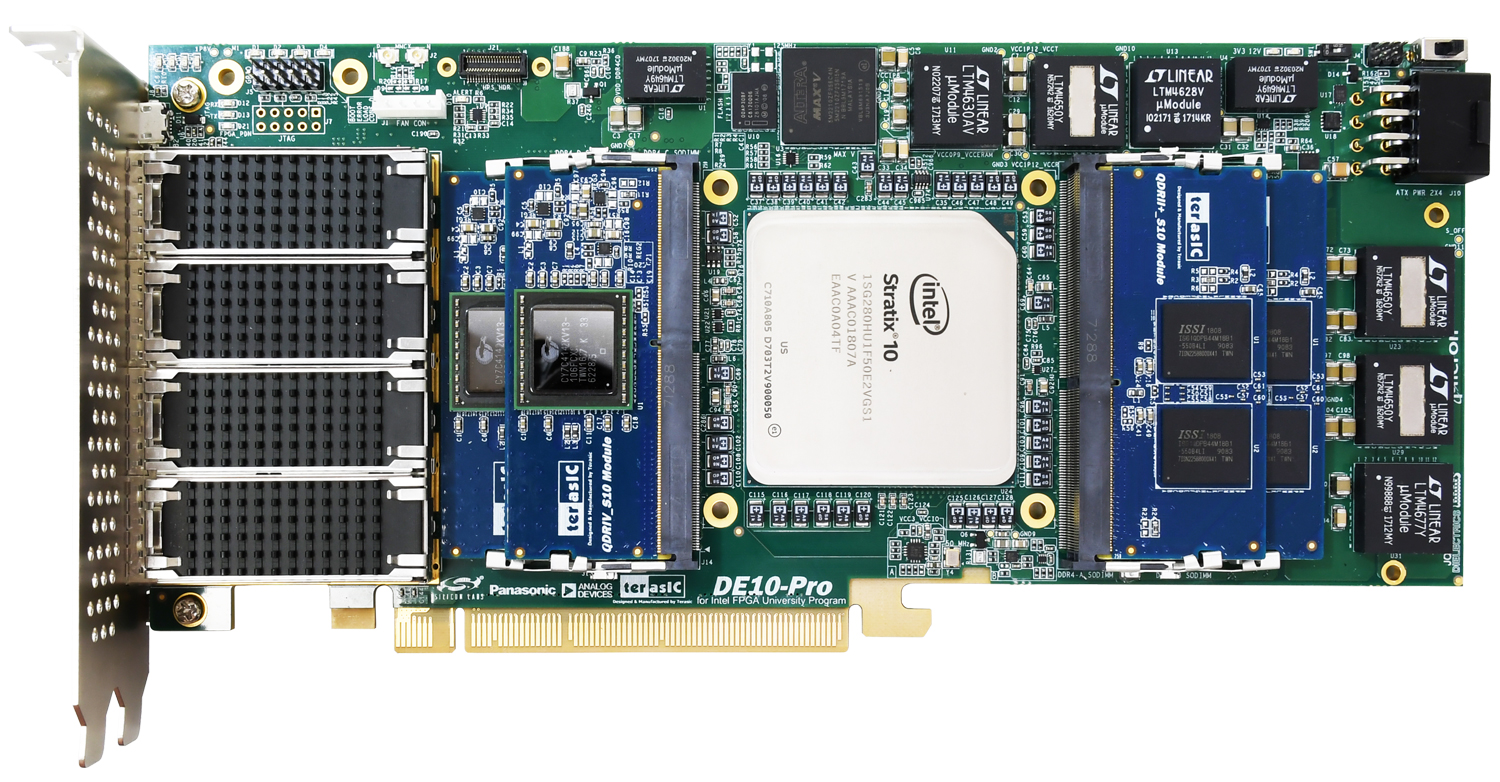

Inspired by the demands of AI, Data Center, and High Performance Computing, Terasic’s DE10-PRO is purpose-built for acceleration and high-speed connectivity applications to address the demands of the next-generation high-performance systems. The board itself takes advantage of the latest Intel® Stratix® 10 to obtain speed and power breakthrough (with up to 70% lower power). Also, armed with 32GB DDR4 memory module running at over 150 Gbps, up to 15.754 GB/s data transfer via PCIe Gen 3 x16 edge between FPGA and host PC, and 4 on-board QSFP28 connectors, the board delivers more than 2X the performance of previous generation acceleration cards. The DE10-PRO fully supports Intel Open VINO™ toolkit to provide optimal Computer Vision and Deep Learning solutions. Our clients' systems can achieve highest computing performance and lowest cost for their AI applications by leveraging the Stratix® 10 FPGA on DE10-PRO.

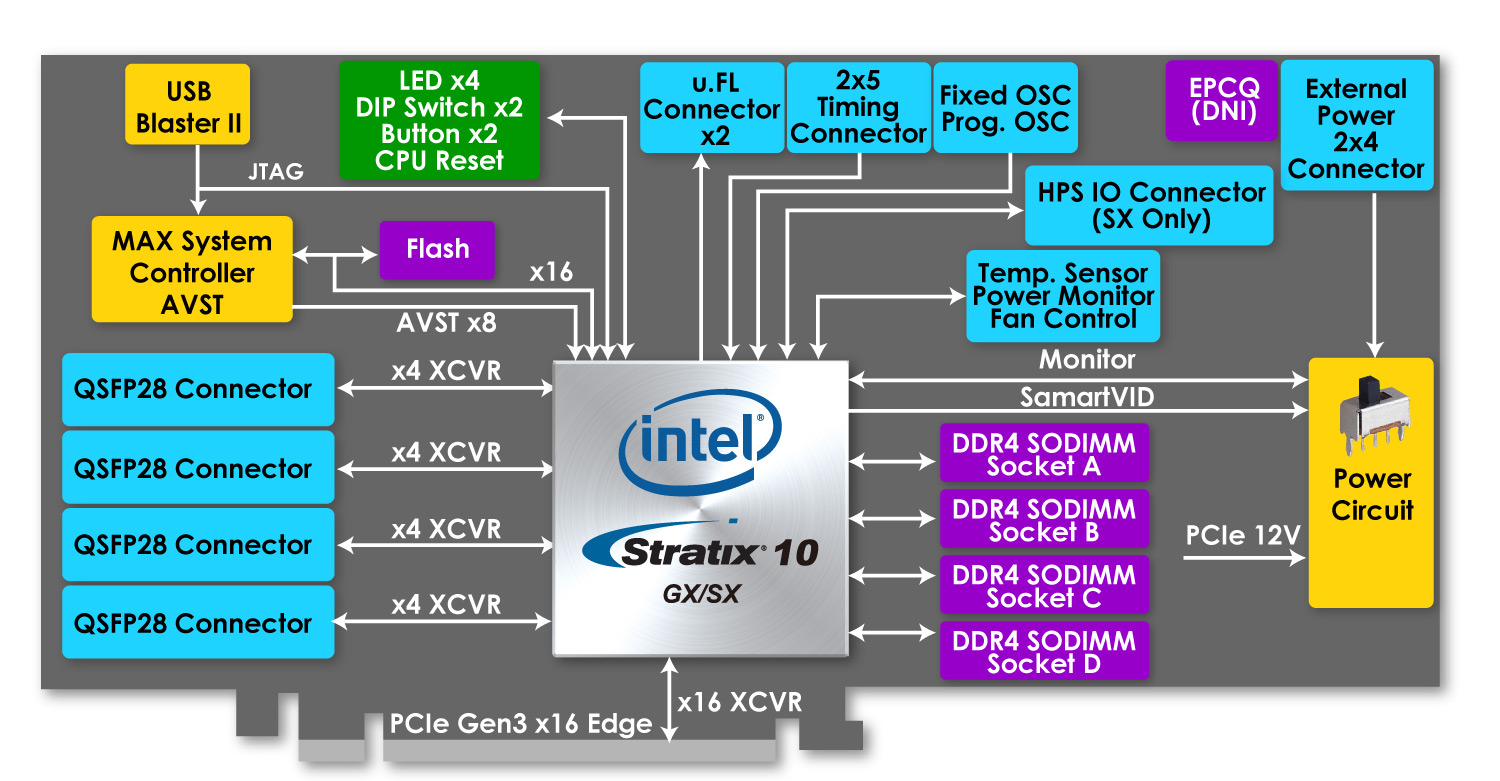

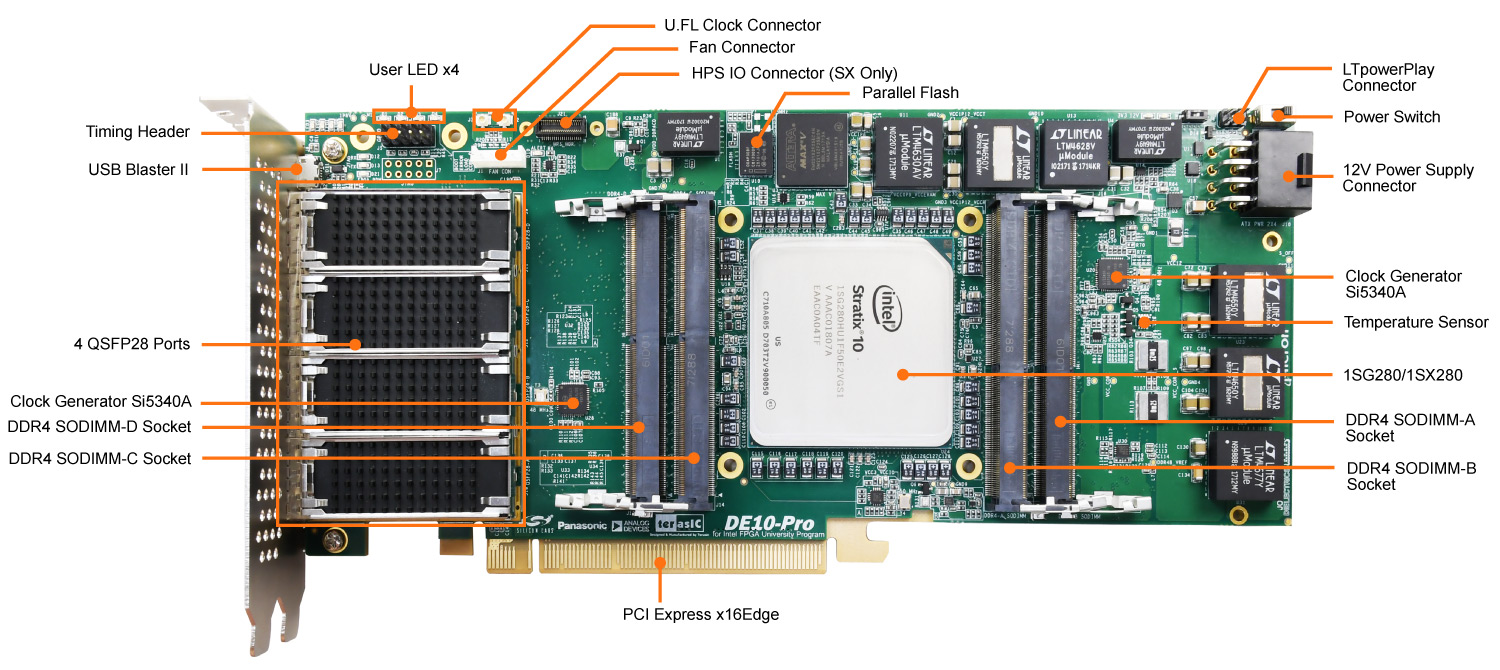

FPGA- Intel Stratix 10 GX/SX FPGA

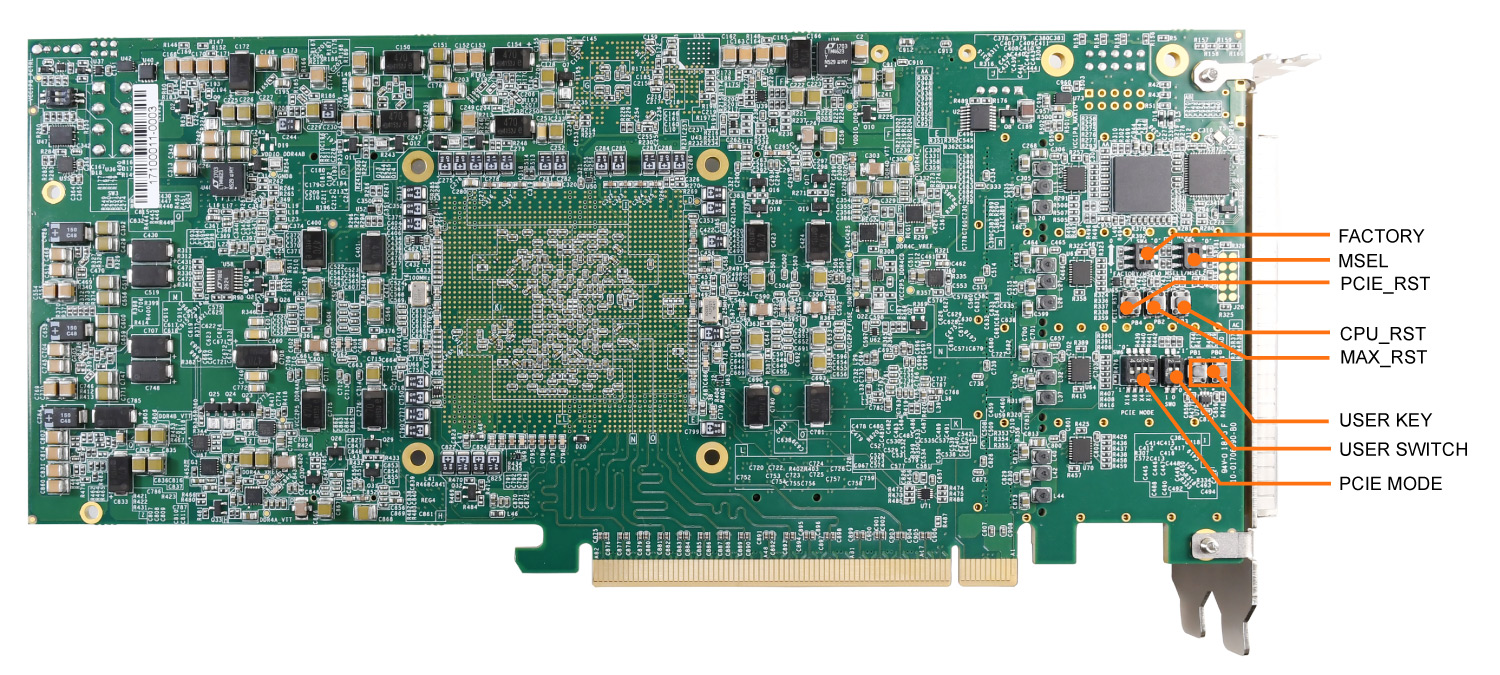

FPGA Configuration- On-Board USB Blaster II or JTAG header for FPGA programming

- Avalon-ST (AVST x8) configuration via MAX II CPLD and CFI flash memory

Memory- 128MB FLASH

- 4 independent DDR4 SODIMM sockets with ECC, up to 8 GB 1200MHz for each socket

Communication and Expansion- Four QSFP28 connectors

- PCI Express Gen3 x16 edge connector (includes PCIe drivers)

- 2x5 Timing expansion header

Others- General user input / output:

- 4 LEDs

- 2 push-buttons

- 2 slide switches

- U.FL clock input / output

- On-Board Clock

- 50MHz Oscillator

- Programmable Clock Generator

- System Monitor and Control

- Temperature sensor

- Power Monitor

- Fan control

- Power

- PCI Express 2x4 power connector for 12V DC Input

- PCI Express edge connector power

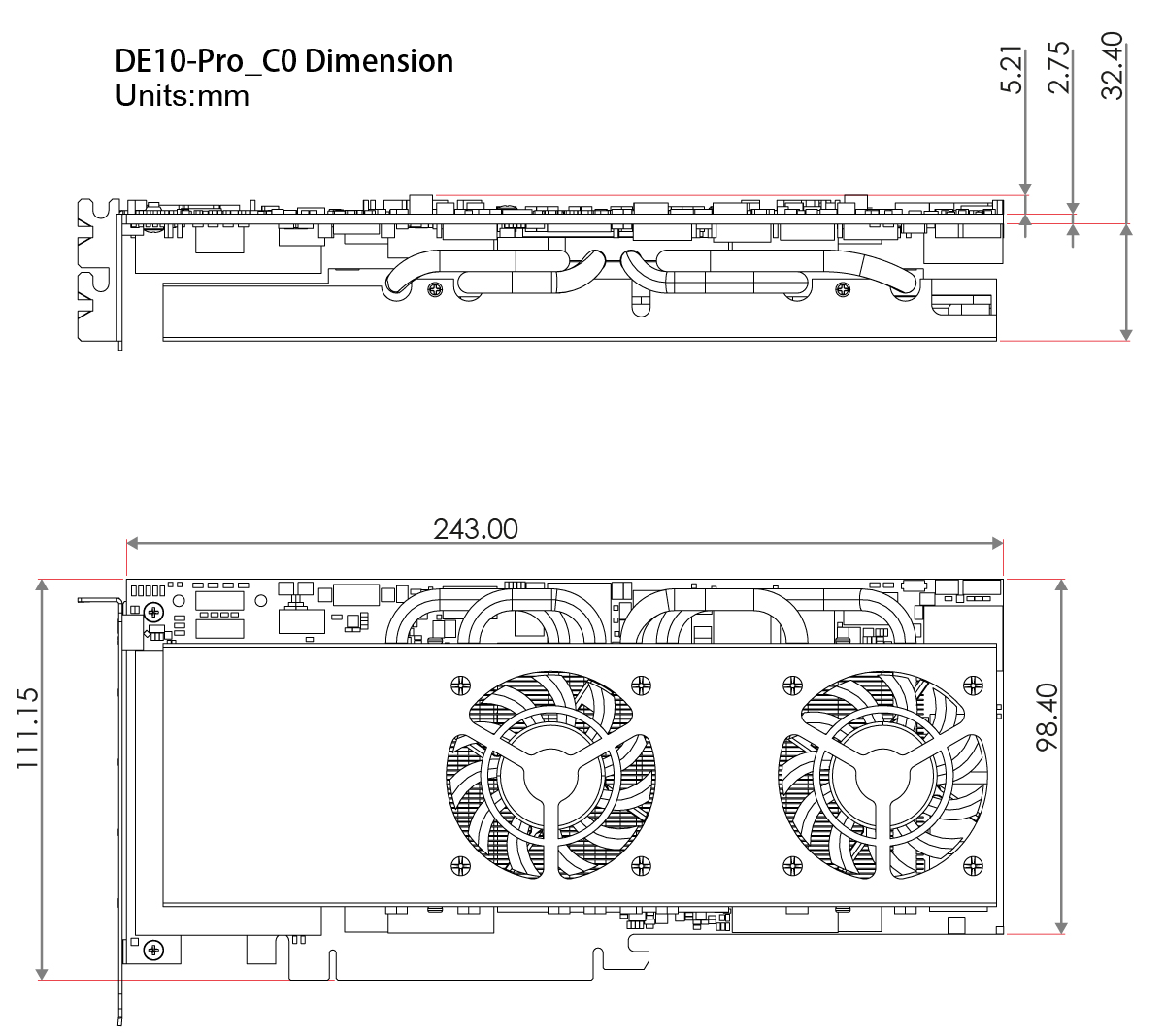

- Mechanical Specification

- PCI Express standard height and 3/4-length

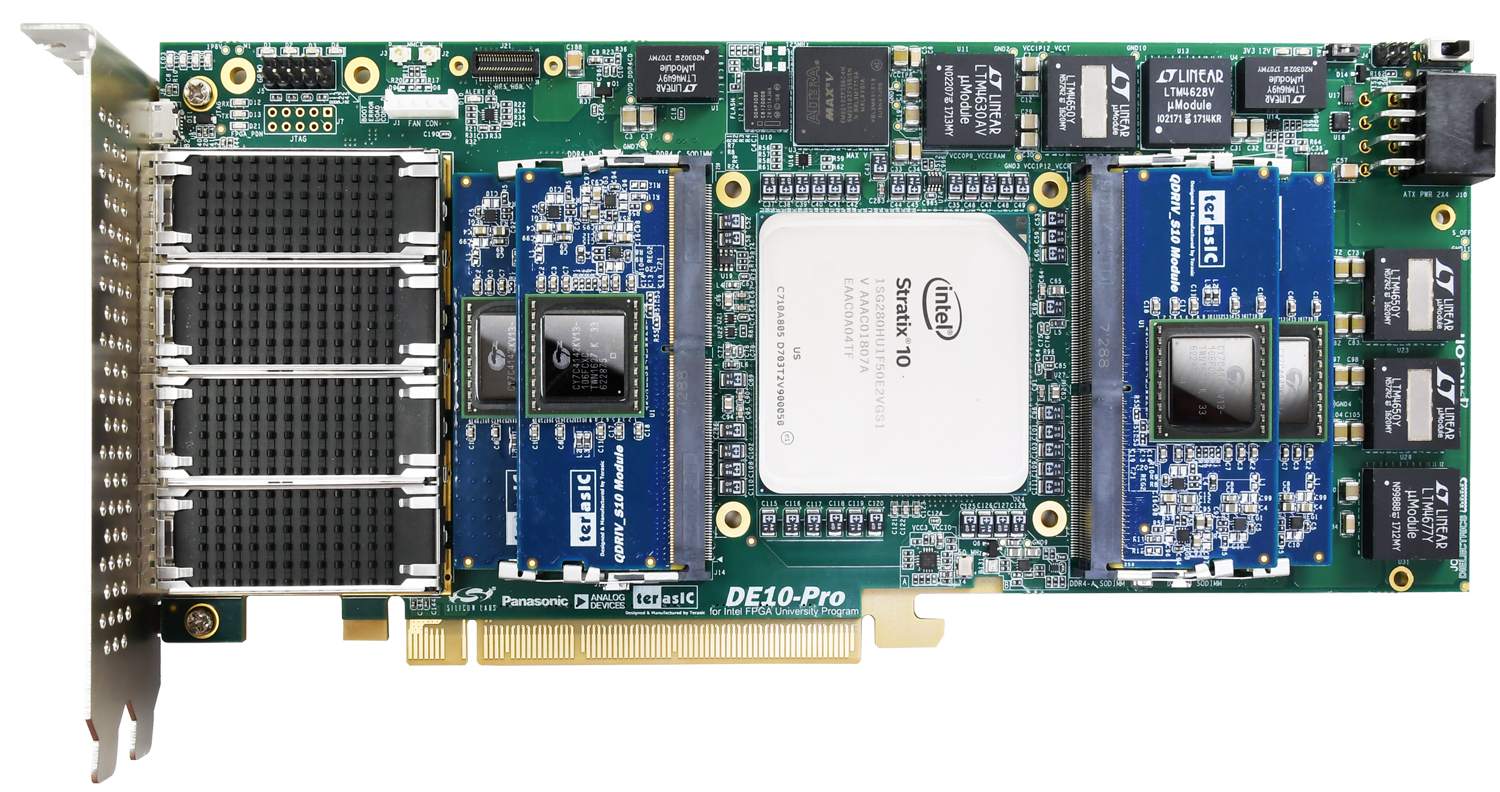

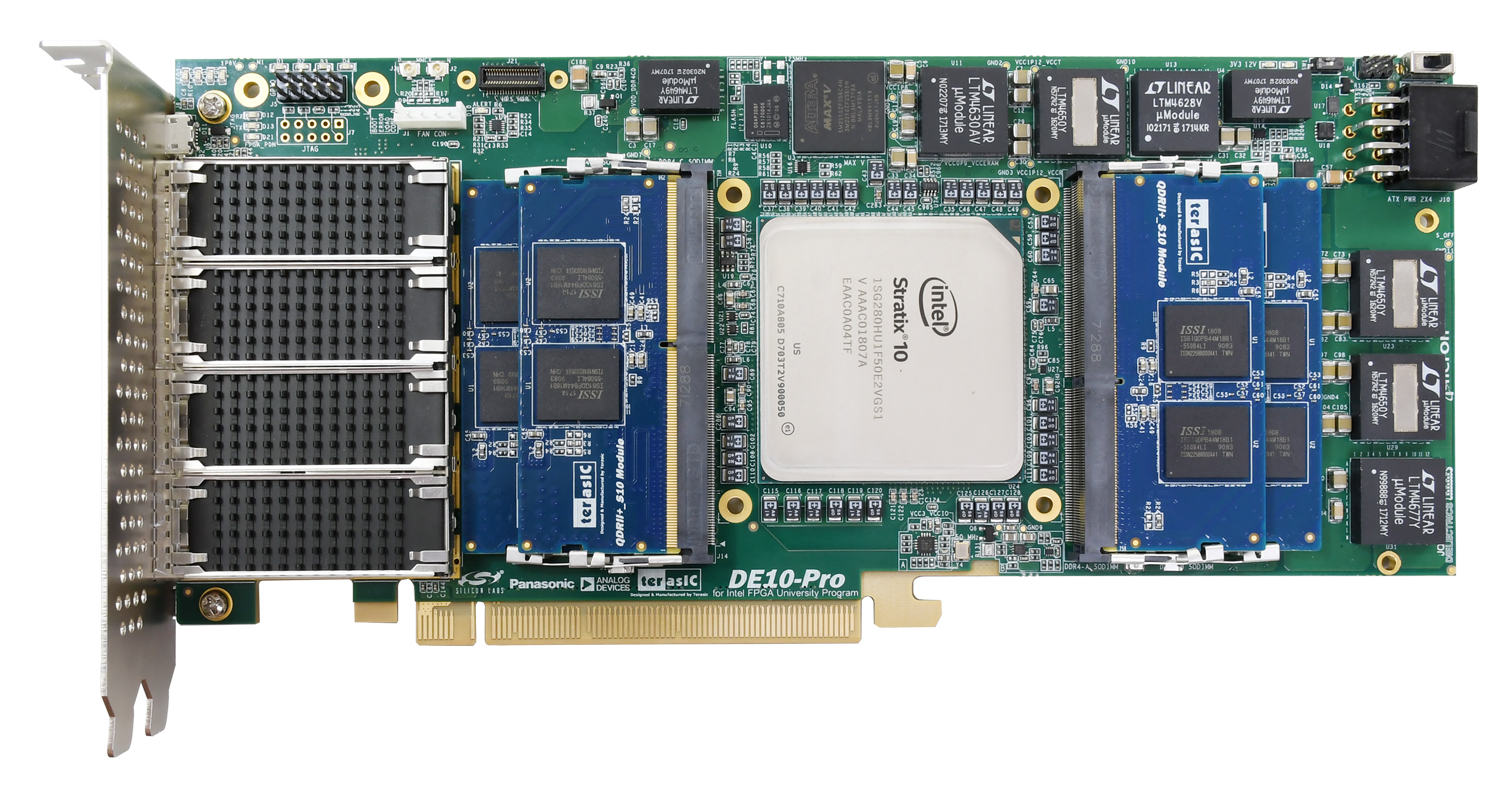

Supported Memory Modules for Sockets- DDR4-2666/2400 for FPGA Core Speed 1/2 FPGA

- QDRII+ 550MHz 144MBits

- QDRIV 1066MHz 144MBits

Block Diagram

Note, DDR4A is shared with FPGA and HPS.

Memory SocketsThe four DDR4 SODIMM sockets are divided into two groups.

For better user flexibility, two different memory modules can be inserted separately in right & left groups. For example, users can insert two DDR4 modules on the right side and two QDRII+ SRAM modules on the left side.

Limitation: The two SODIMM sockets must be inserted with the same memory to prevent dysfunction on memory module that requires higher voltage.

- Two QDR-IV Modules, two QDR-II+ Modules

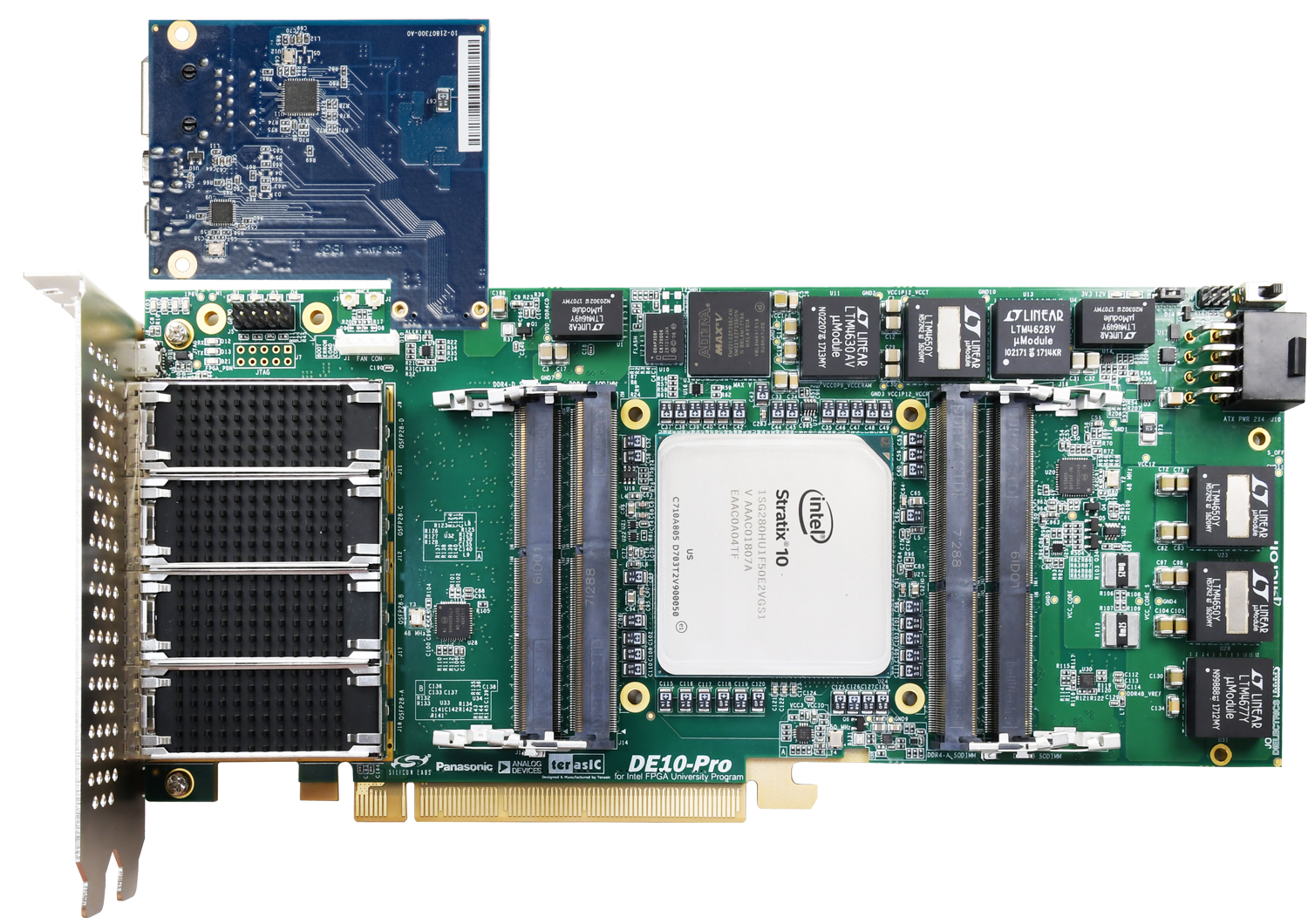

HPS Daughter Card

- Board Size: 106.65 X 243 mm

- DE10-Pro Development Board

- DDR4 ECC SO-DIMM Module x4 (Installed)

- PCIe Bracket (Installed)

- Air Cooler (Installed)

- Power Supply & Power Cable

- AC Power Cord

- USB to Micro USB Cable

- Screw & Copper Pillar Package

- DE10-Pro Quick Start Guide

- S10-HPS Daughter Card (HPS Only)

Quartus design software license is not included in this kit.

|